588 results found for ""

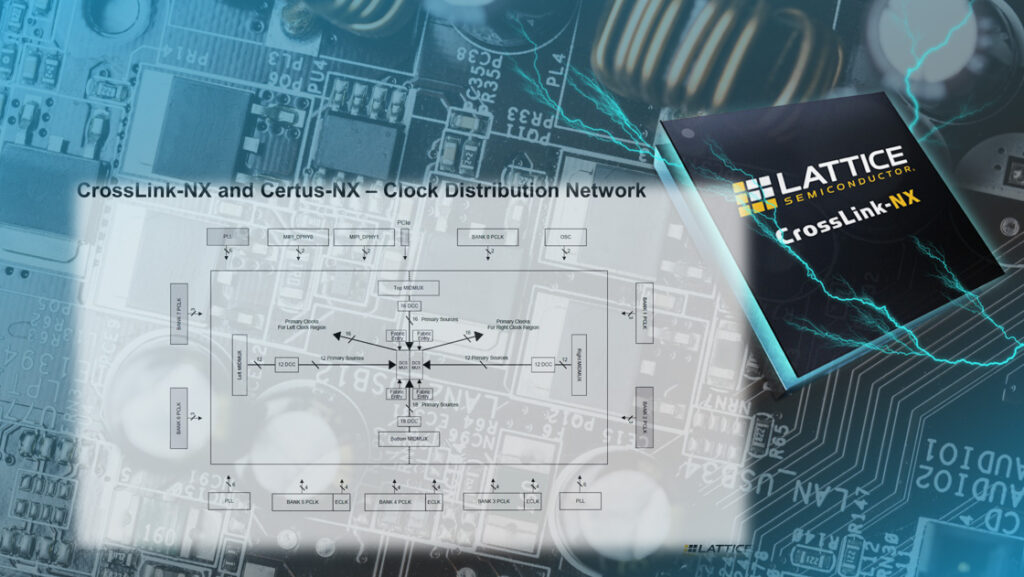

CrossLink-NX: Architecture – On-chip oscillators, Global PLL, Clock Distribution Network

Intermediate

·

9mins

1 Credit

Learn about the clocking structures and clock network. In this module, we cover the on-chip internal oscillator, Global PLL, primary clocks and edge clocks. The blocks covered here apply to the Lattice CrossLink-NX, Certus-NX and CertusPro-NX devices.

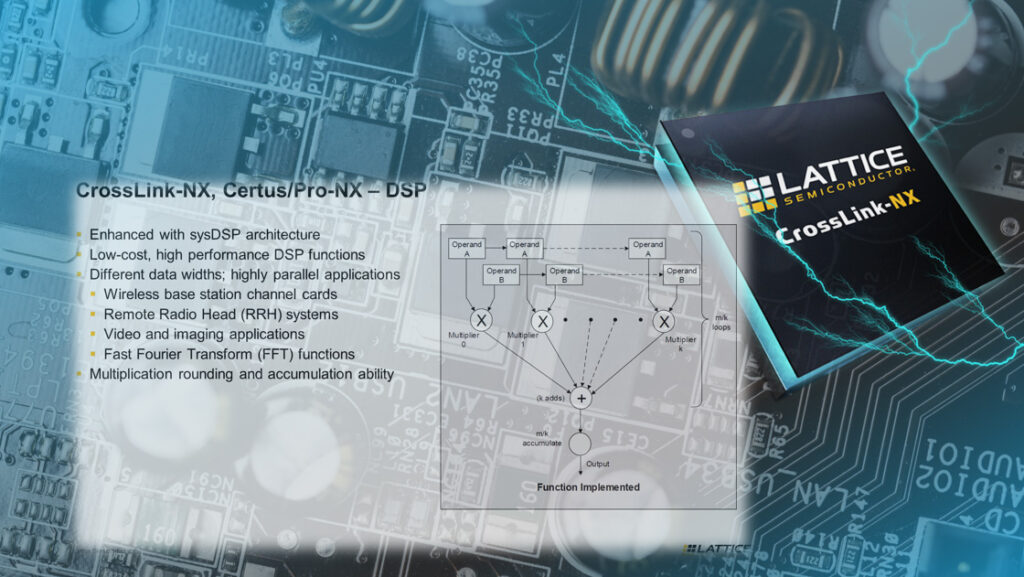

CrossLink-NX: Architecture – Digital Signal Processing (DSP) blocks

Intermediate

·

7mins

1 Credit

In this module, we go over the sysDSP or digital signal processing block, including the available DSP primitives and supported operations. The DSP block covered here applies to the Lattice CrossLink-NX, Certus-NX and CertusPro-NX devices.

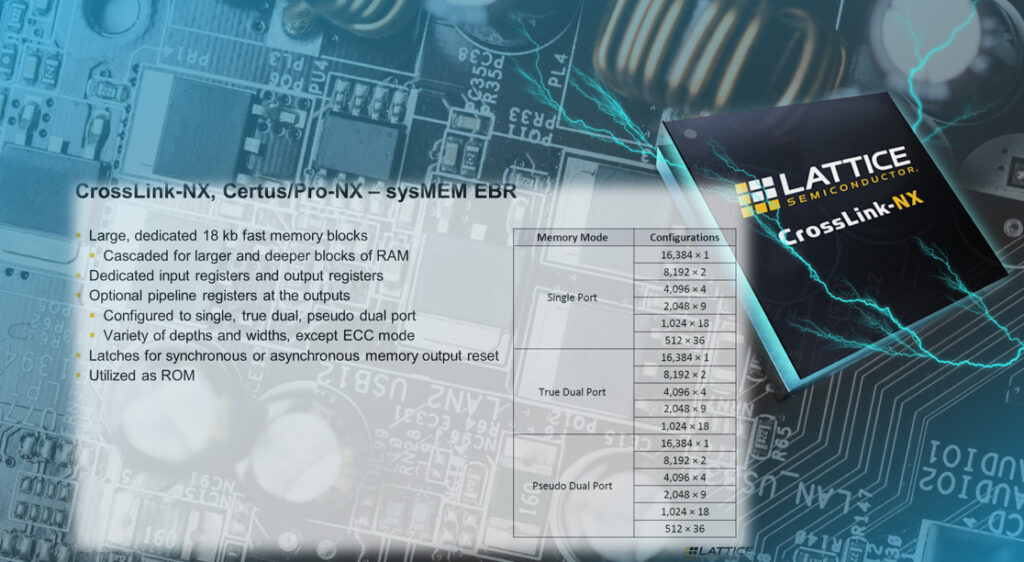

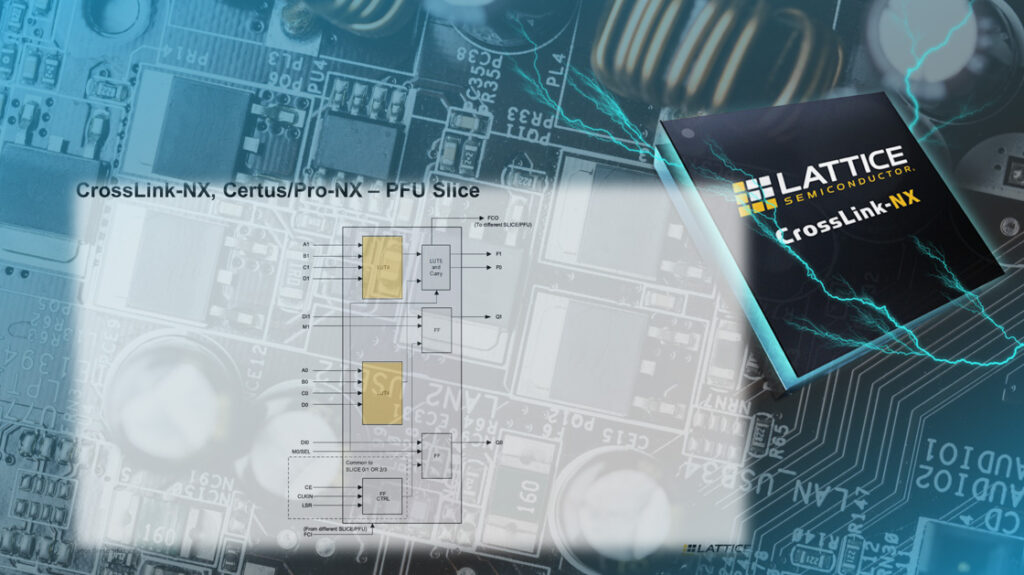

CrossLink-NX: Architecture – Programmable Functional Unit (PFU)

Intermediate

·

4mins

1 Credit

Learn about the programmable functional unit (PFU) block, the structure of the PFU slice, and its various supported modes and features. The PFU block covered here applies to the Lattice CrossLink-NX, Certus-NX and CertusPro-NX devices.

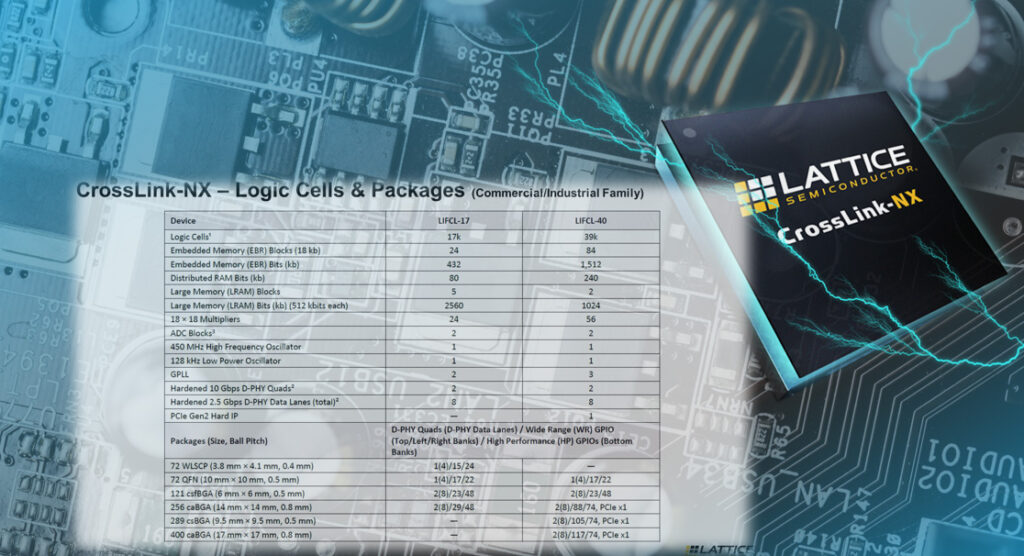

CrossLink-NX: Family Plan, Architecture – Course Introduction

Intermediate

·

3mins

1 Credit

Preview the CrossLink-NX Device Architecture course content, and the CrossLink-NX family plan.

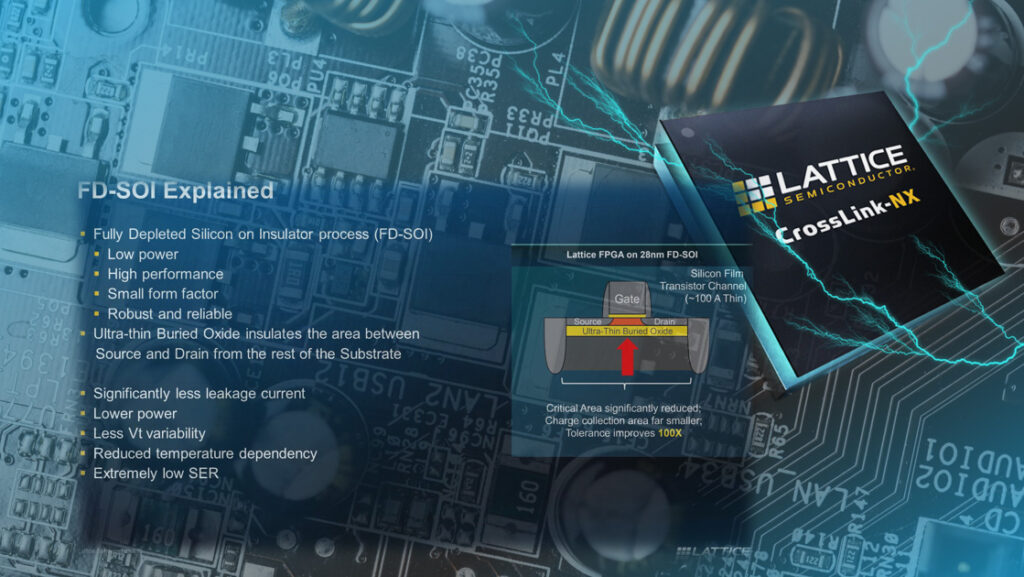

Nexus Family: Architecture – FD-SOI

Intermediate

·

1mins

1 Credit

Understand how the FD-SOI technology is making a difference to the devices built on the Nexus platform.

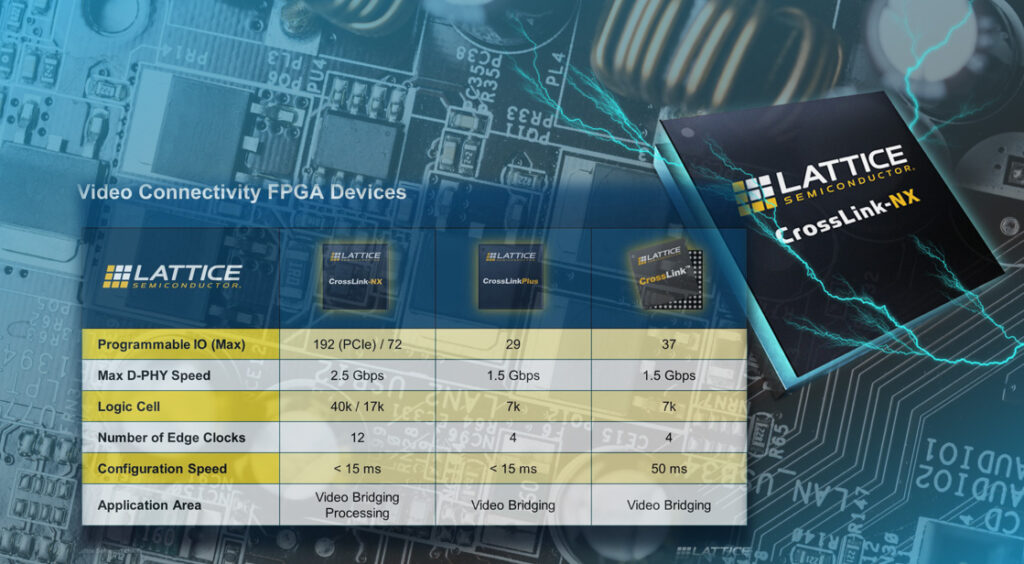

Lattice: Product Portfolio – Video Connectivity FPGAs

Intermediate

·

2mins

1 Credit

Get familiarized with the Lattice FPGA portfolio, as well as some of the features that the upgraded Lattice CrossLink-NX offers, in comparison to its predecessors in the video connectivity family.

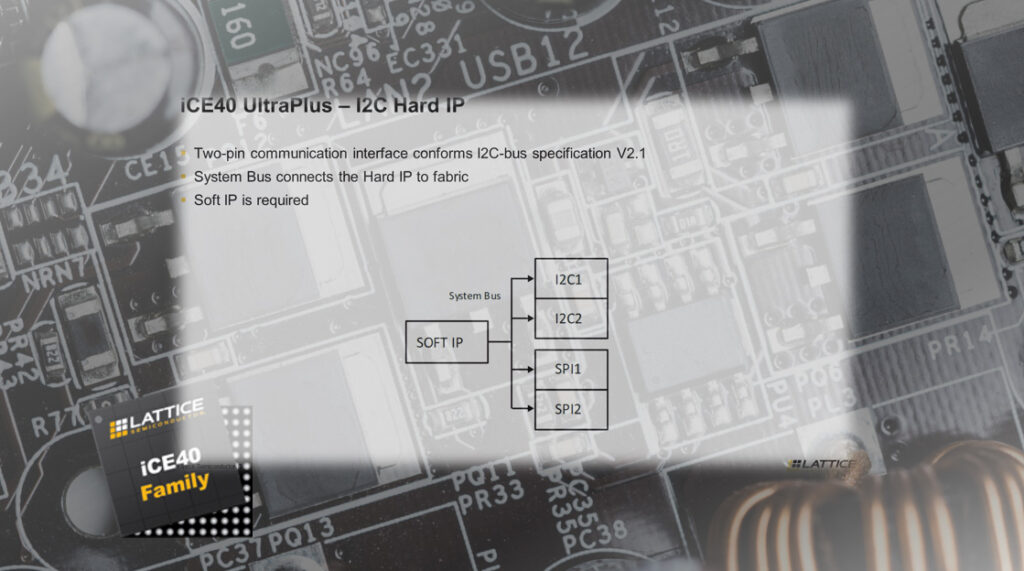

iCE40 UltraPlus: Architecture – I2C & SPI Hard IPs, Configuration & Programming

Intermediate

·

7mins

1 Credit

Understand the functionality of the I2C and SPI hard IPs on the Lattice iCE40 UltraPlus. This module also provides details regarding device configuration and programming, including usage of the Non-Volatile Configuration Memory (NVCM).

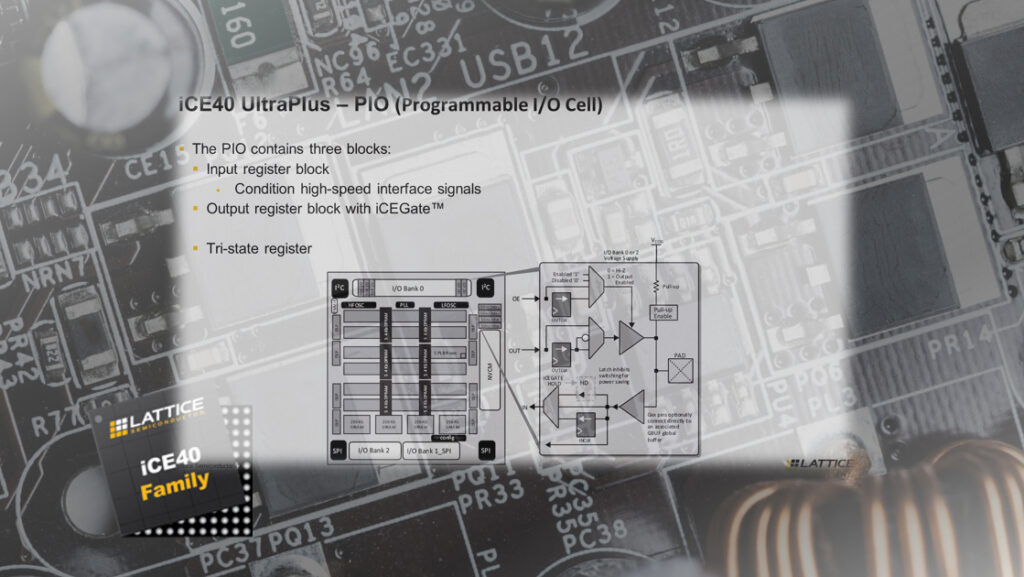

iCE40 UltraPlus: Architecture – sysI/O, Programmable I/O Cell (PIC), Pulse-Width Modulator (PWM) IP

Intermediate

·

9mins

1 Credit

Learn about the I/O and interfaces available on the Lattice iCE40 UltraPlus, including the sysI/O banks (which includes the Programmable I/O Cell (PIO)), RGB High Current Drive I/O pins, and Pulse-Width Modulator (PWM) IP.

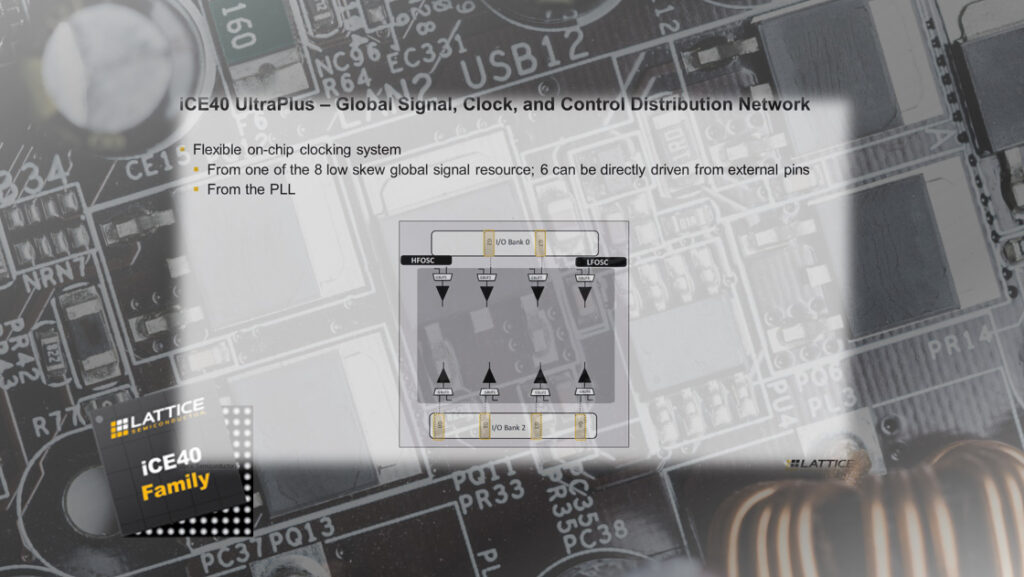

iCE40 UltraPlus: Architecture – PLL, Clock Distribution Network

Intermediate

·

9mins

1 Credit

Learn about the architecture of the PLL block, and the Clock Distribution Network (which includes the global signals, global clock, and control distribution network).