59 results found for ""

FPGA Reset: Summary and Best Practices

Basic

·

4mins

Free

This module summarizes all important information and the best practices when using resets in your designs.

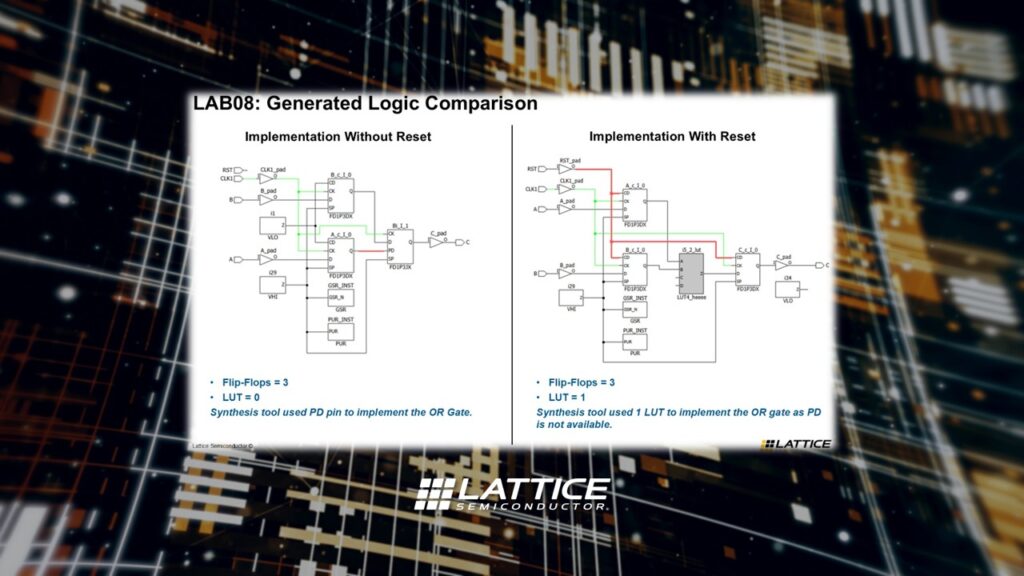

FPGA Reset: Impact on Design Optimization

Basic

·

9mins

Free

Examine how the use of resets in design impact design optimization along with lab activities.

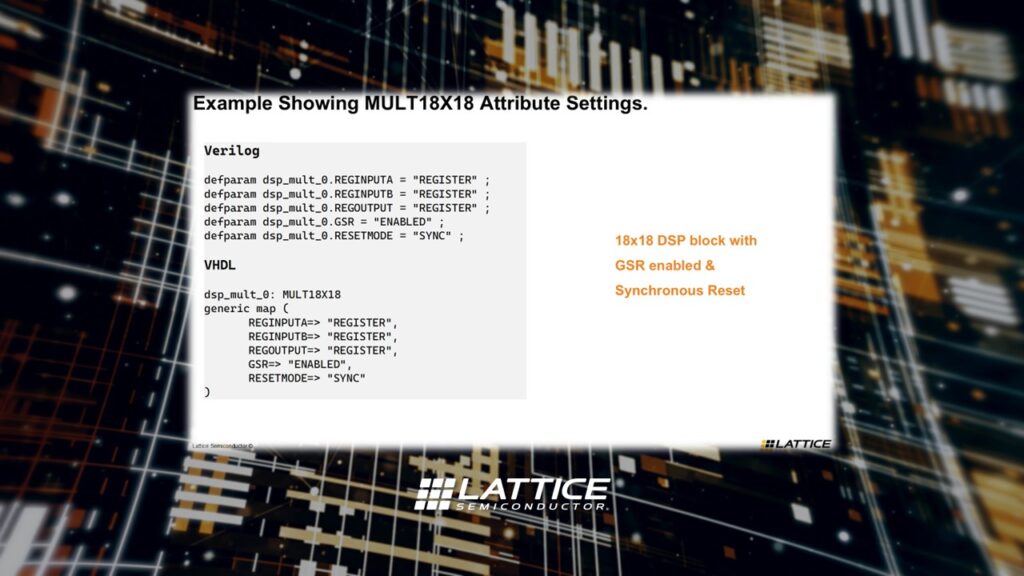

FPGA Reset – Hardware Architecture: FPGA Primitives

Basic

·

3mins

Free

This module discusses how reset is implemented in other FPGA primitives such as flip flops, memory blocks and DSP blocks.

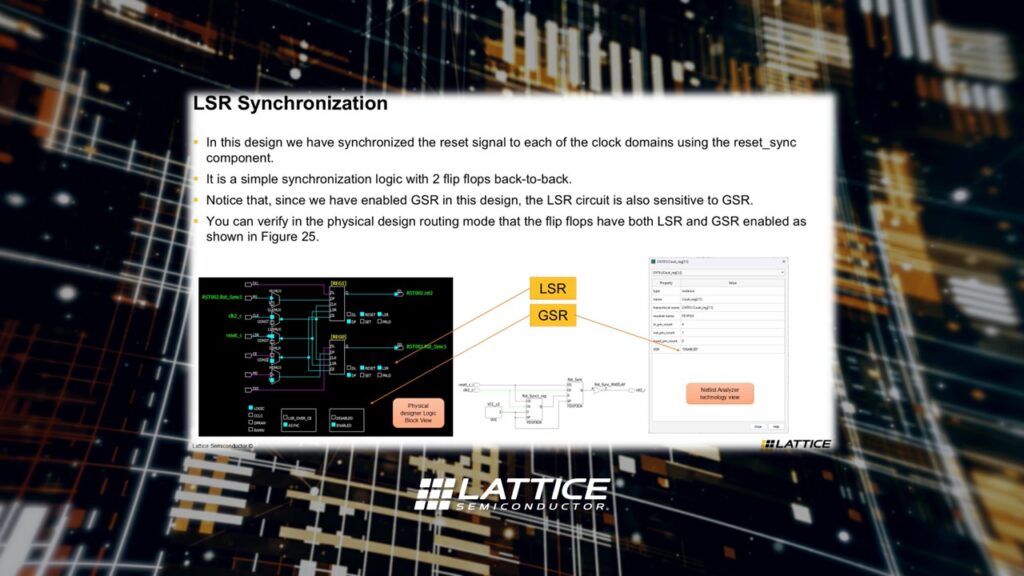

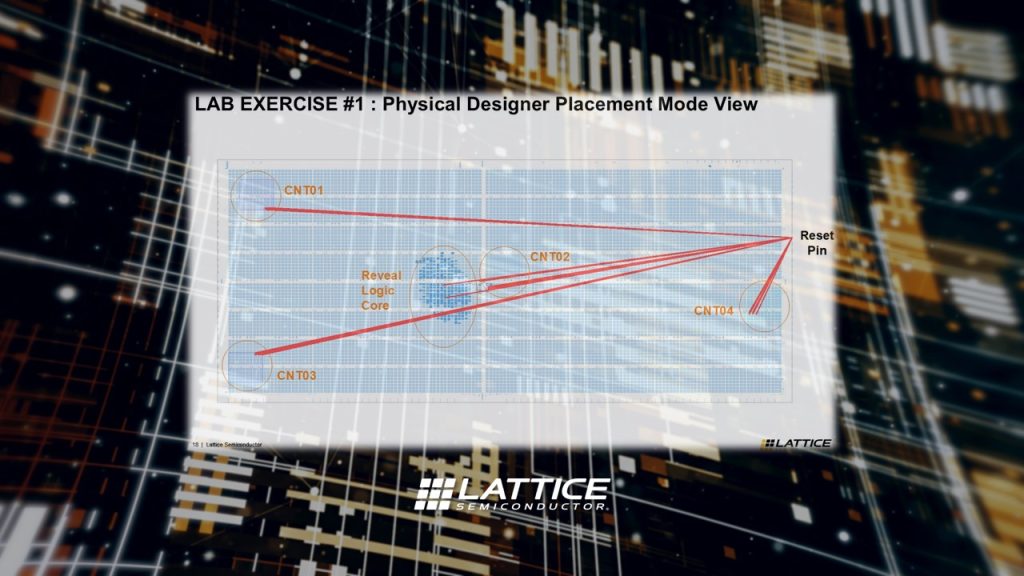

FPGA Reset – Hardware Architecture: GSR vs LSR

Basic

·

10mins

Free

Understand the differences between GSR and LSR and their advantages and disadvantages in hardware implementation.

FPGA Reset – Hardware Architecture: Introduction

Basic

·

1mins

Free

This module gives and introduction on how reset, set or preset are implemented in hardware architecture.

FPGA Reset: Global Set Reset

Basic

·

2mins

Free

This module introduces the global set reset which is a common dedicated resource in FPGAs.

FPGA Reset: Introductions to Reset Concepts, Timing, and Architecture

Basic

·

9mins

Free

This module covers fundamental reset concepts, discussing why resets are needed, types of resets, and their impact on system stability and reliability.

FPGA Reset: Reset Role in Timing Closure

Basic

·

6mins

Free

Examine the role of reset signals on timing closure, addressing timing parameters and metastability issues that arise from improper reset handling.

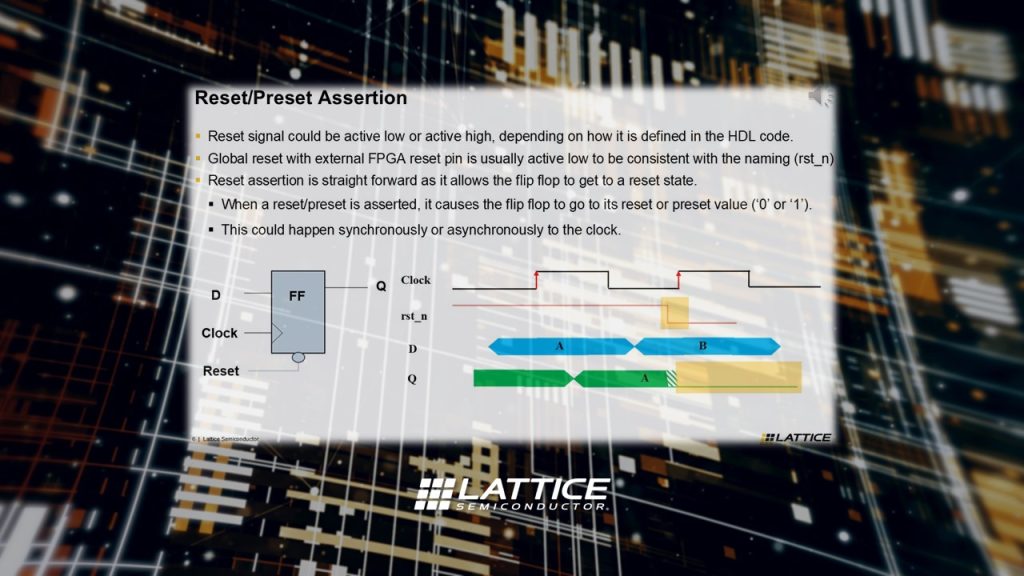

FPGA Reset: Asynchronous Reset

Basic

·

12mins

Free

This module discusses asynchronous resets, focusing on its implementation, potential challenges like timing violations, and techniques to minimize metastability risks.

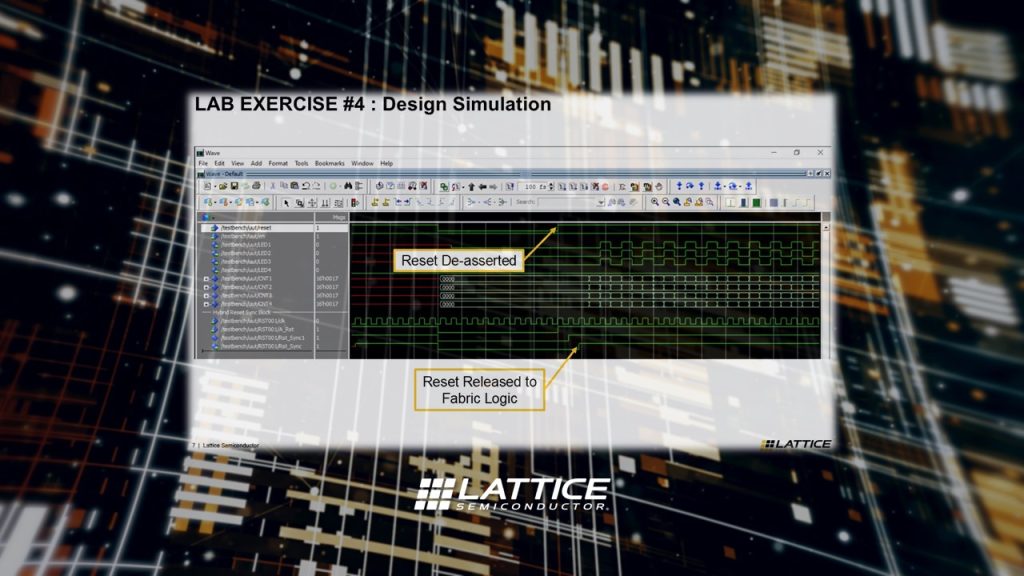

FPGA Reset: Hybrid Reset

Basic

·

3mins

Free

Introduces the hybrid reset approach, combining asynchronous assertion with synchronous de-assertion to enhance reliability and reduce timing issues.