167 results found for ""

Lattice Advanced

Intermediate

·

15hrs 48mins

Free

This certification program is designed for professionals looking to deepen their understanding of Lattice product architectures, Radiant, Propel and Diamond software tools features, and Lattice solutions stacks and architectures.

Timing Constraints Deep Dive with Radiant: Radiant vs Diamond

Intermediate

·

5mins

2 Credit

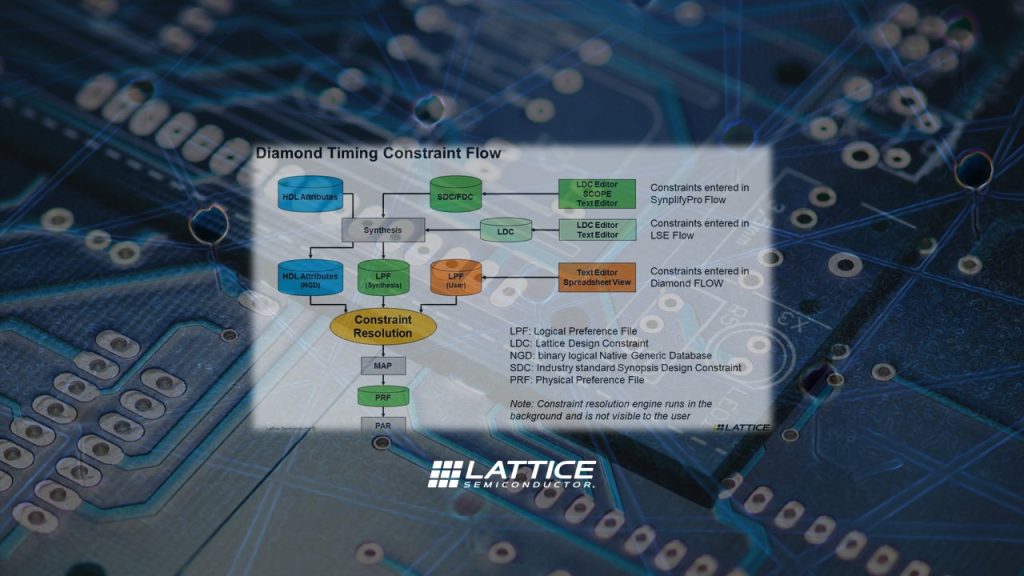

If you are migrating your designs from Diamond to Radiant, this module will help you differentiate their differences in handling timing constraints and how to prepare for the migration.

Timing Constraints Deep Dive with Radiant: Timing Constraint Methodology

Intermediate

·

5mins

2 Credit

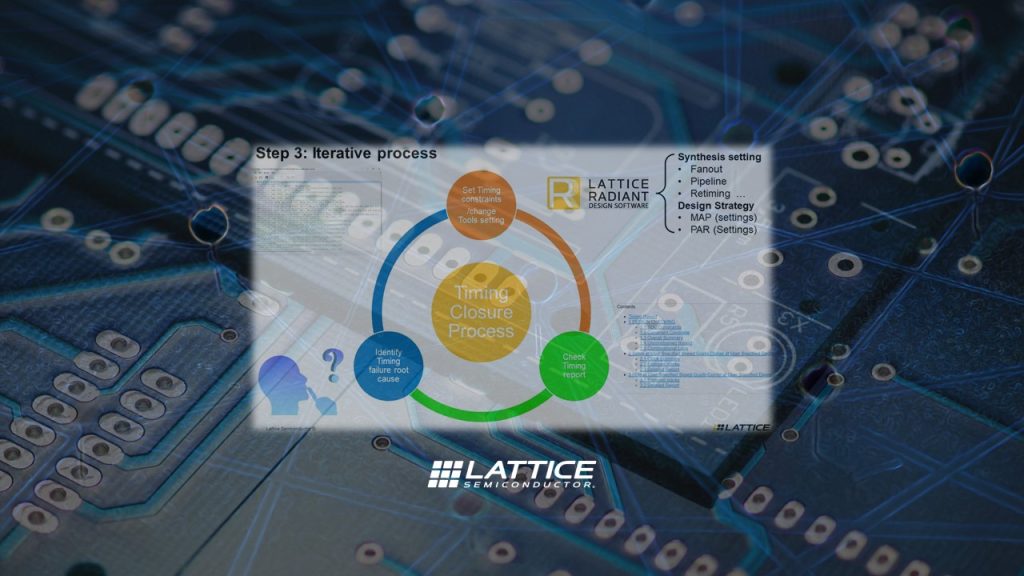

In this module, we will propose a three-step process for handling timing constraints, ensuring high constraint coverage, and achieving the best timing results for your design.

Timing Constraints Deep Dive with Radiant: Constraint Priorities and Resolution

Intermediate

·

5mins

2 Credit

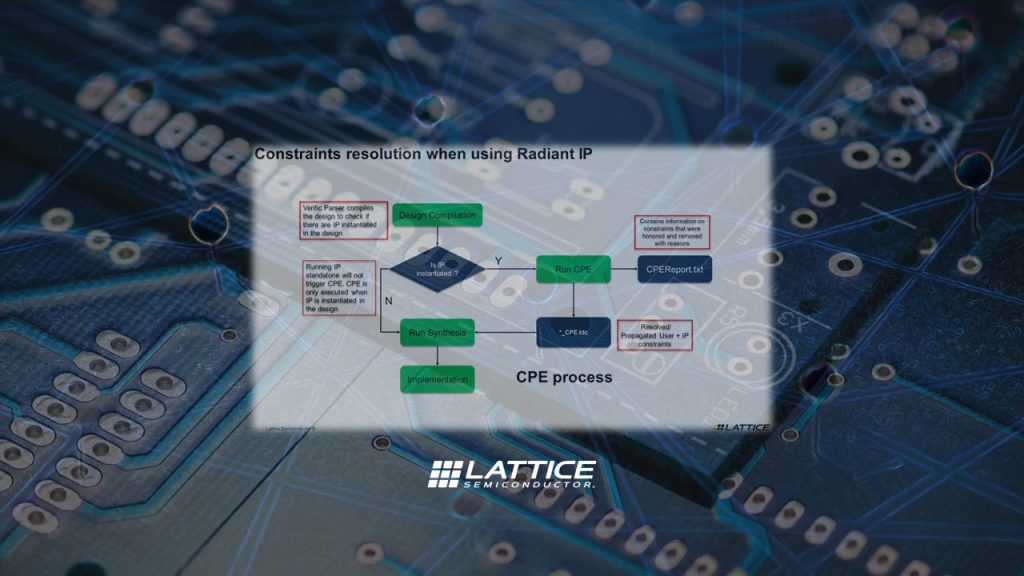

Uncover how Radiant software prioritizes multiple constraints and the rules it applies to resolve constraint conflicts.

Timing Constraints Deep Dive with Radiant: Timing Exceptions

Intermediate

·

13mins

2 Credit

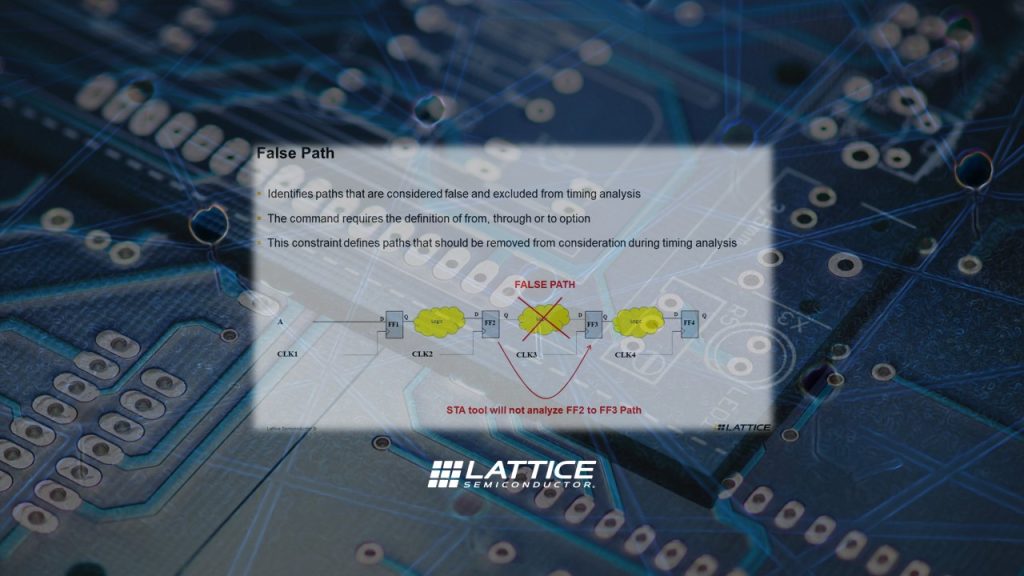

Understand more about timing exception constraints, which can help improve your design timing by excluding, relaxing, or even further constraining specific paths in the design.

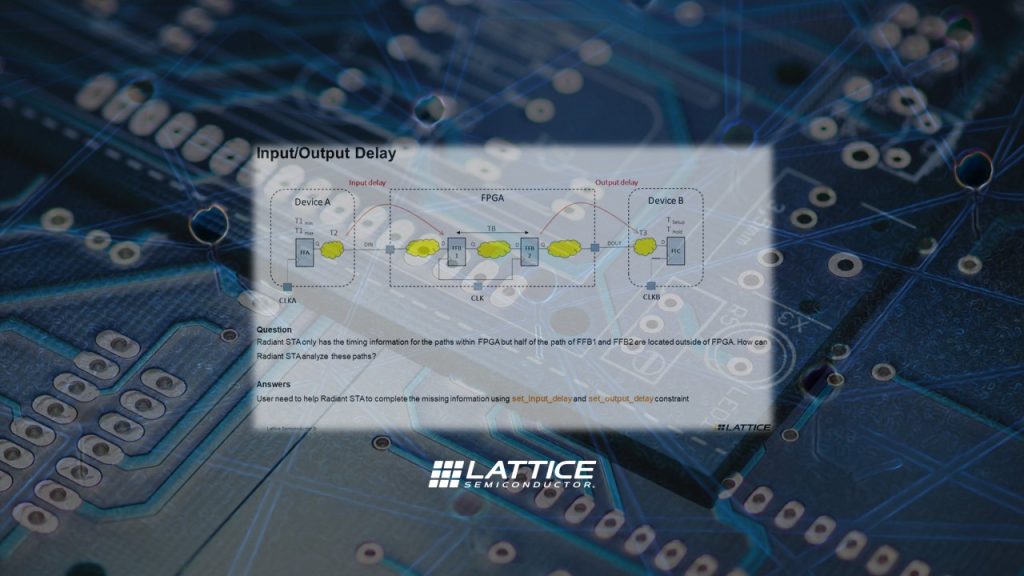

Timing Constraints Deep Dive with Radiant: Types of Timing Constraints (Part 2)

Intermediate

·

6mins

2 Credit

This module will review the different boundary constraints, their syntax, and how and where to use them with practical examples.

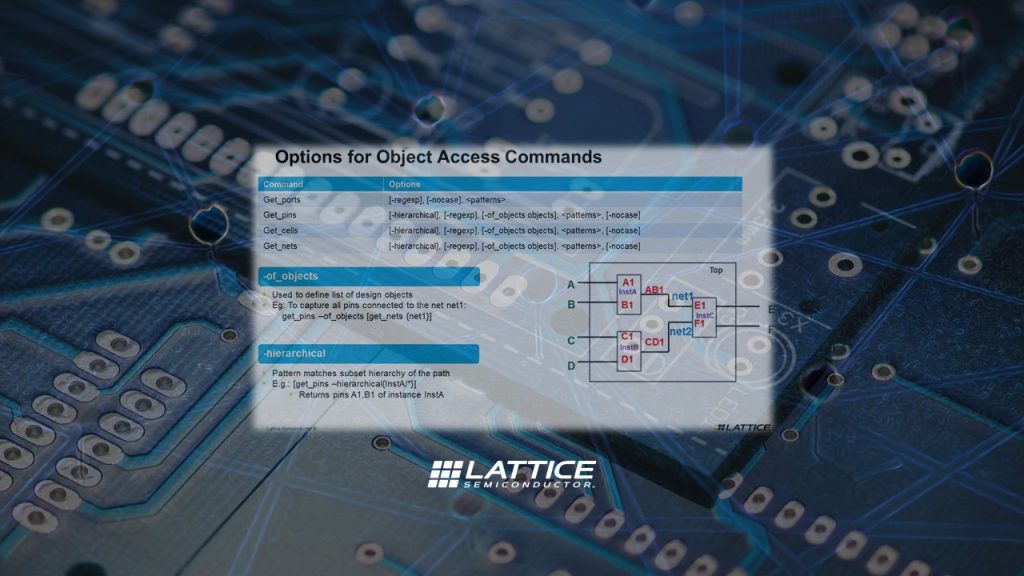

Timing Constraints Deep Dive with Radiant: Types of Timing Constraints (Part 1)

Intermediate

·

14mins

2 Credit

This module will review the different clock constraints, their syntax, and how and where to use them with practical examples.

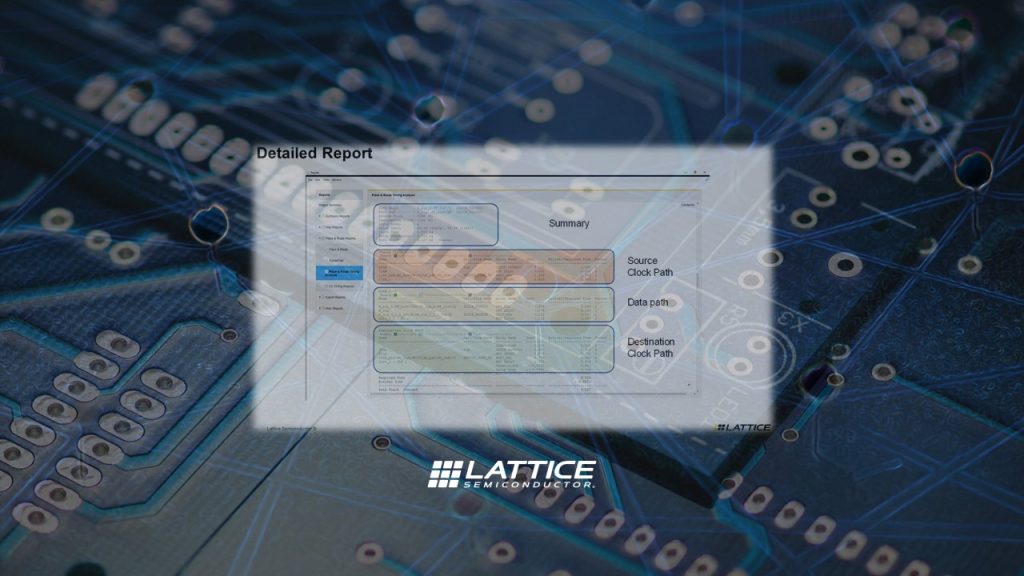

Timing Constraints Deep Dive with Radiant: Timing Constraints in Software Tools (Part 5)

Intermediate

·

9mins

2 Credit

This demonstration will walk you through the timing analysis report contents and other cross-probing tools described in the previous module.

Timing Constraints Deep Dive with Radiant: Timing Constraints in Software Tools (Part 4)

Intermediate

·

5mins

2 Credit

Explore the static timing analysis reports and other Radiant tools, which can help you understand and improve your design timing.

Timing Constraints Deep Dive with Radiant: Timing Constraints in Software Tools (Part 3)

Intermediate

·

11mins

2 Credit

This module will help you gain an in-depth understanding of setup time and hold time analysis. It will cover scenarios with same-clock and clock domain crossings.